随着AI、5G通信以及云计算等专用计算领域的发展,面向专用计算领域的计算机体系结构也进入了新的黄金时代。描绘这一黄金时代的两支重要画笔就是开源硬件(芯片)与敏捷开发:开源可降低芯片设计门槛,敏捷设计能缩短开发周期。

开源指令集RISC-V引发了开源硬件的热潮。但芯片的设计和生产流程比软件更长,需要更多工具和流程,EDA也开始转向依靠开源社区的模式来解决复杂的设计难题,同时降低开发成本。但国内EDA技术一直是一项软肋,本土EDA企业尚未发展壮大,该如何应对开源EDA这一新的技术形态与生态模式呢?这些问题在5月14日下午召开的中国计算机学会青年精英大会(YEF2021)技术论坛【芯片智造——敏捷设计与开源EDA之路】上展开了激烈的讨论。

说到开源芯片,RISC-V可谓是开源的代表。去年RISC-V国际基金会将总部搬往瑞士,目前其已有超过1000个会员,企业机构约200家。中国在这里面占据很重要的作用,中国企业占比超过20%,而且19个理事会成员中有9个来自中国。随着开放指令集RISC-V逐渐受到业界追捧,开源芯片的概念逐渐进入人们的视野,并受到全世界的关注与投入。国际上,早在2019年国际计算机体系结构旗舰会议ISCA的远景研讨会上,包括图灵奖得主David Patterson教授在内的多位美国工程院院士,以及来自MIT、UC Berkeley、UCSD、Stanford、Google、Nvidia、DARPA等顶尖大学、企业和政府机构的专家就聚焦讨论了“面向下一代计算的敏捷开放硬件”的前沿热点,涉及到内容包括指令集、EDA工具链开源、设计流程、高层次综合、形式化验证。看向国内,“十四五”规划也已开始对开源芯片布局,“十四五”规划第五篇第十五章第一节中提到,支持数字技术开源社区等创新联合体发展,完善开源知识产权和法律体系,鼓励企业开放软件源代码、硬件设计和应用服务。那么开源芯片有哪些创新机会呢?中国科学院计算技术研究所副所长包云岗在技术论坛上讲到:RISC-V属于指令集开放,其实是指令集手册的开放,如英特尔CPU的指令集手册有5000多页,ARM CPU的指令集手册有2000多页,而RISC-V的指令集手册只有200多页。如果把指令集变成真正的架构,此时就会产生诸多设计文档,那么文档可以公开;根据设计文档再变成源代码,源码也可以公开;EDA工具链可以将开源代码再变成芯片版图,那么EDA设计工具也可以开源。他总结,开源芯片主要包含有三个层次:(1)指令集(2)处理器微架构设计/实现(3)设计流程/工具。在这三个层次中,除了指令集,芯片设计的工具也很重要。EDA工具是开源芯片设计体现的基石,如今多种开源EDA工具基本覆盖了芯片设计中的模拟仿真、逻辑综合、布局布线、物理实现和签核等功能。众所周知,全球EDA市场被三大厂商Cadence、Synopsys、Mentor(2021年1月更名为:Siemens EDA,即西门子EDA)垄断。他们的规模大,产品线完整,可以提供全流程的完整解决方案。相反,国内EDA工具在中国的市场份额不到5%,在全球的市场份额仅为0.2%。而且国内EDA公司规模小,产品单一,多是“点”工具,只能提供局部解决方案。单一EDA工具很难满足设计人员对于IC设计的全流程需求,不同工具间的切换又为数据完整性增添了风险。于是日前市场对于开源平台的呼声日益增高。

鹏城实验室、中科院计算所的解壁伟认为,开源EDA是支撑开放芯片生态的重要保障。多个成功经验表明,开源开放是构建繁荣的技术生态和产业生态的必要基础。如Linux操作系统,支撑了整个开源生态体系;再比如Android移动操作系统,虽然现在已经闭源,但当年以开源为起点,统一了除iOS外的整个移动互联网生态;在人工智能领域,Caffe、TensorFlow、Pytorch、PaddlePaddle可以说是整个AI技术生态体系的基石。开源EDA工具可以降低芯片设计门槛,如降低芯片设计的人力、IP、EDA成本。还能为开展EDA领域的基础科学研究和人才培养,无论是对企业、高校、学术科研机构还是芯片和EDA方向的个人爱好者而言,都能提供很好的思路。如果开源EDA可以集合多方力量,将有助于我国加速追赶国际先进水平。然而,我国EDA软件的基础还相对薄弱,在开源领域几近空白。开源EDA仍然面临诸多挑战:用户少、贡献者少以及框架结构不清晰;论坛上也讨论了一些解决方案。具体如下:(一)用户少:开源EDA工具质量相比商业工具有较大差距,用户数量非常有限。解决方案是提升工具质量,强调生产环境下的项目检验,即开源EDA工具不能只停留在学术论文和软件代码,要与其他点工具共同汇聚成工具链,支撑完整的芯片流片验证,产生有效的用户反馈。如美国的Magic就经过了数次流片验证,论文就有实际芯片测试数据。(二)贡献者少:EDA领域相对小众,其开源社区更是人丁单薄,Yosys、abc、magic、OpenROAD等开源工具的主要贡献者大多在10余人左右。由于EDA学科的特点,开源EDA贡献者需要同时具备CS、Math、EE和MicroE的知识,技术门槛较高。每个开源EDA工具的开发并不开放,基本是某个学校、研究机构和公司的内部团队,外部参与者很少、也很难参与。解决方法是充分拆解、抽象和描述EDA技术问题,并分类转化到数学、算法和高性能等专业领域能够理解的语言表述,发动多个学科的社区力量。(三)框架结构不清晰:代码不统一且复用率低是开源软件的一项通病,然而开源EDA工具与算法强绑定,问题更为突出。设计新算法通常需要大量重写代码,失去了开源的意义。解决方案有二。第一,模块化设计,从基础框架设计出发,再深入到算法层,抽象共有操作和数据格式,从代码中探索出迭代重构规律,形成精简高效和模块化的基础框架。这种模块化设计还便于用分布式并行计算架构进行EDA设计流程的加速。第二,规范化抽象,用Multi-level Intermediate Representation(MLIR)等优秀的编译器设计理念对整个设计流程(尤其是前端设计)进行多个抽象层次的划分,便于各个领域专家专注于各自的抽象层次,同时通过多个层次的编译打通EDA工具链,完成敏捷方便的全流程验证。这样,即使一个点工具也可以通过规范的转换格式,灵活的接入到开源的EDA工具链中,完整地验证自己所开发工具的性能和质量。目前,北美产业界和学术界正在形成这种趋势。落实到开源EDA项目来说,无论从低工艺(110nm)至高工艺(55nm,40nm甚至28nm)。从高校教学级应用到企业产品级应用,从小规模ASIC芯片到更大规模的SoC项目,都应坚持研用结合的策略,以实用为牵引,以用带研,研以致用。从工具链、点工具、基准测试集、示范应用以及工业级开源工艺库等五大方面逐个击破。

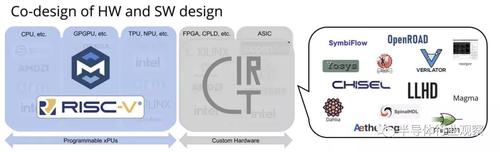

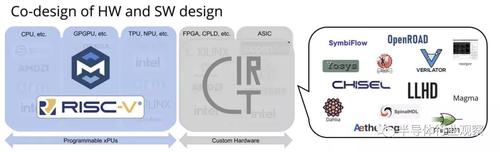

值得一提的是,在ASPLOS 2021大会上,刚刚从Google Brain跳槽到明星RISC-V公司SiFive的Chris Lattner博士(LLVM 项目的主要发起人与作者之一, Clang编译器的作者)做了The Golden Age of Compiler Design in an Era of HW/SW Co-design的演讲,提出了基于MLIR编译技术打造的全新的统一的EDA (Electronic Design Automation)框架,像软件中的TensorFlow或PyTorch那样为EDA设计工具链提供完整、灵活的基础设施。CIRCT项目与MLIR同源,在硬件设计和软件编译的容易形成生态一致性。

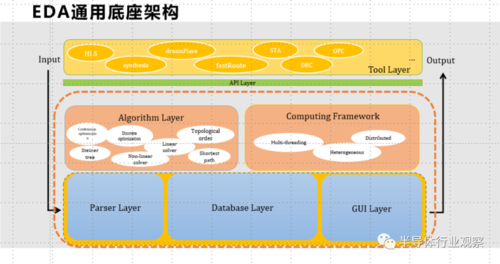

在开源EDA软件之路上,国内EDA学术和产业都在努力寻找合适的位置为开源EDA做贡献。在开源芯片领域,中科院计算所2019年启动了RISC-V处理器芯片与RISC-V原生操作系统等项目,并且在国产28nm工艺上构建具有性价比优势的开源芯片技术体系。此外,他们还在探索开源EDA设计开源芯片,基于现有开源工具,构建了一套基于Python的RTL到GDSⅡ的设计流程;去年8月份,国科大五位本科生整整历时两年使用开源EDA工具设计出了果壳-1芯片,并实现了流片。中科院还研发了芯片敏捷设计云平台AgileServe,该平台集成了各种开源要素,能支持用户快速定制处理器芯片与软件开发,降低芯片设计门槛。于学生来说,可以随时随地开展芯片设计;对老师来说,可以实现在线指导学生。南京集成电路设计服务产业创新中心有限公司(以下简称EDA创新中心)常务副总经理陈刚介绍了以开源的方式来打造国产EDA通用底座(openEDI)。考虑到国内的EDA点工具各自独立,建设国内生态的通用底座,有望把点工具连接在一起。EDA通用底座的研发目标是支持所有国产EDA工具,聚合成套的EDA工具链,成为国内生态的通用底座。下图为EDA通用底座架构。最下方的部分是数据层,承载所有EDA在内存及磁盘上的数据库和数据模型,其中包括各种解析器的模块、用户界面模块等。上层为通用算法层与计算框架。北京大学的林亦波在会上介绍了知名的《深度学习辅助布局布线优化》项目,他讲述了利用深度学习来改进传统的布局布线算法,在这个过程中必须要利用开源的布局布线工具,否则很难获取深度学习样本。未来他们将继续改进算法,提高稳定性和泛化能力。预计可能发布如ImageNet那样的开放EDA数据集,吸引学术界和产业界的共同竞争与发展。东南大学国家专用集成电路系统工程技术研究中心的闫浩讲述了宽电压近阈值设计方法学研究与开源EDA的进展。他介绍到,EDA工具的技术挑战是不断演进的工艺和蚀刻尺寸带来的偏差建模以及优化算法的开发。他指出在做研究时,遇到最大的挑战是需要耗费大量精力复现别人代码,因此他们也与如NiiCEDA等国内EDA企业合作,积极投入到开源时序分析工具的开发中。宁波大学的储著飞分享了在多逻辑域自动综合工具上的研究进展。他讲到,逻辑综合是在满足约束条件下,将所有设计数字电路的RTL级描述,转化为指定的工艺库中单元电路的连接。逻辑综合主要包括三个阶段:翻译、优化和工艺映射。他指出,不同的逻辑完备集所发展而来的综合方法适用场景不同,现有的这些EDA工具都是基于传统布尔逻辑发展而来,新型算符能带来更多机会,比如基于极性变换的Reed-Muller、TB和RM双逻辑等。在EDA开源方面,他指出逻辑综合工具的发展趋势:一、AI for EDA,用AI的方法推断逻辑综合优化变换的顺序,让没有任何经验的工程师得到一个优化脚本;二、EDA for AI,用查找表形式反推逻辑操作,达到与神经网络训练权重一样的目的;三、Optimal Solution,给定一个数字电路,现有的方法高度依赖SAT求解器获得如最小节点个数,最小逻辑深度等最优解,但是SAT 求解器本身又是启发式算法,通过数字电路仿真可以辅助SAT进行更高效的搜索;四、Technology Enabler,发展新的逻辑抽象方法,帮助一些诸如二维材料等新工艺的评估和发展。无论训练集,搜索优化与新模型都将在开源生态中获得收益。

开源EDA生态从0到1所面临诸多困难,如何打通开源EDA的生态闭环?如何维护生态持续发展?如何防范流片失败、IP泄露、专利等生态风险?未来又该何去何从?针对这些问题,在场学者和专家众说纷纭,进行了激烈且有意义的讨论。

跟传统的开源软件不同,开源EDA软件的数据结构、代码质量尤其算法的专业性极高,用户群体较小,限制了开源社区的规模。纵观历史,硅谷渺如星辰大海的高科技公司都是从高校创新开始做起的。EDA也一样,首先在高校培养开源EDA的第一批用户群体,包括老师和学生,让他们通过创新的形式先把开源工具用起来,然后通过不断的使用和迭代改进工具,在将来达到可用的程度。然而,从学术界开始推广和维护EDA生态闭环也有挑战。最主要的是发展学术界参与开源EDA和持续维护开源项目的问题。从功利的角度看,当高校研究人员转移研究兴趣或者课题结束时,维持开源项目的动力消失;学生花几年的经历学习和掌握开源EDA工具,不如掌握商业工具对找工作更实用;高质量的开源工作不多,学生们重新实现一个算法或工具有时比hack(甚至debug)一个开源项目的代码更快。学生毕业之后,如果没有一个很好的文档和高质量的代码管理,那么后续的学术继续迭代开发的动力也不足。因此论坛建议适当引导高校的学术评价标准,使代码和文档质量高的开源项目、Github/Gitee等代码托管协作平台上星数多的项目,成为高校学者、学生以及企业专家的学术名片,这对于启动和维护开源EDA项目、对于学生就业将会是极大的激励。开源EDA生态的建立也需要基准测试集,特别是可以完成端到端流程的工业级基准测试集;如何从学术界小规模数据集到工业级先进设计,是个需要继续探讨的话题。业界知名的芯片设计公司能否提供一些脱敏的设计,让开源社区可以以此为参考进行学术研究、学生竞赛,以此扩大开源社区的规模。尤其,在深度学习技术与EDA领域紧密结合的当代,更需要一个芯片设计领域的“ImageNet”来促进社区繁荣。产学研有机联合,提升软件质量,提供开源EDA独有价值

前面也提到的开源代码质量的问题,其实开源EDA工具对软件质量的要求远比其他领域严苛。因为EDA软件与芯片设计紧密结合,一旦设计出有问题的芯片,不仅要修改软件代码,还要重新流片,代价高昂。因此开源EDA软件无法像互联网/游戏软件那样,用敏捷开发模式、低成本试错迭代模式提高软件质量。学术界的开源项目要与EDA、IP等工业界有机地联合。高校的老师和学生启动项目并实现原型,企业提供工程力量和资金用于维护和推广,业界的工程与品控能力可以保障开源软件的质量和持续发展。业界不仅可以吸收开源项目的精髓,提升自己的产品先进性,而且还做了一个极好的广告,在人才市场中形成良好口碑。典型的案例就是美国DARPA项目的openROAD开源项目,Cadence参与度甚至远高于学术界综合。放眼望去,美国成功的开源项目(LLVM,TVM等)最终都得到了业界的大力支持。为实现高校与企业的有机联合,开源EDA工具必须能提供独特的价值,例如对新的设计方法或者新的制造工艺更为敏锐,提供与商业工具互补的功能特性。维护EDA生态闭环,项目的定位、以及组织者联结需求、资源、人员的作用十分重要。风险与机会并存,合理区分风险,降低整体芯片开发成本

EDA生态在技术标准、安全可信、以及流片风险均存在风险。IEEE标准有成熟的运作规范,相对安全。但很多事实标准其实是三大EDA公司的私有标准。即使在开源社区有可免费使用的私有标准,也存在着跟标准相关的隐藏专利风险。需要制定国内标准,并掌握关键技术来防范专利风险。开源EDA软件的可信和安全则是一把双刃剑。一方面,开源EDA工具中可能存在恶意代码泄露用户的核心设计数据,也可能在设计里植入恶意的硬件木马;另一方面,EDA工具代码开源,且贡献者基本可以溯源,相关责任也容易追查,一切都在阳光下风险反而可控。针对流片失败的风险,可能并非开源EDA工具独有问题。要在指甲盖大小的硅片上摆放上百亿个几纳米大小的晶体管是当今世界最具有挑战的工程,流片失败本身是不可避免。商业公司的EDA工具也不一定能保证成功,特别是支持新技术新工艺的工具。开源许可证有免责声明,应让使用开源工具进行流片的使用方充分认清风险和成本。成功流片的开源EDA工具,反而是高质量的最佳宣传,有机会培育出大量以设计服务为目标的公司,凭借开源工具的使用经验帮助用户提高流片成功率,有望降低整体的芯片开发和设计成本。对开源EDA工具的各种风险,需要区别对待,随着开源EDA工具实践经验增加,反复评估风险变化。EDA生态子系统协同,寻找可持续的动力,形成价值链闭环

开源EDA生态有学术、企业等内部生态子系统。高校立足教学和科研,适合做创新工作,产生有独特功能、技术超前的开源EDA工具,获取学术影响力;只要这些独特的“优势”可以转化成企业明确利益需求,就会在企业转化为一个高质量的产品级项目。但这些产品级项目不一定会重新开源。应该寻找一种激励企业的模式,在其保护商业价值的同时,能持续对共性技术部分保持开放,让学术界能在更高质量的EDA工具平台上继续贡献。为此,可以考虑GPL许可证模式,强迫新增和修改共性功能代码开源,再通过封装成云服务等形式来约束GPL的作用范围,保障企业的投入和产出公平。开源EDA生态应与外部生态合作共赢。例如,与超算和云计算的生态融合,既能解决EDA软件算法需要消耗大量算力的问题,促进超算中心的业务发展;也可以借助云服务吸引更多的工具用户,降低使用获取和使用门槛,同时也促进云计算厂商的用户群。Google和微软的EDA上云就是非常典型的案例。

本次论坛由CCF YOCSEF上海AC组织,执行主席为CCF YOCSEF上海主席(2021-2022)蒋力,副主席(2020-2021)裴颂文,论坛思辨和闭门讨论分别由北京大学罗国杰、浙江大学卓成共同主持。论坛吸引了50余位高校学者、企业专家与研究生参加。后续我们还会继续组织敏捷设计,框架与编译器等专题论坛,与开源EDA,开源硬件开放指令集关系紧密,敬请关注。